Technical Approach

As power consumption of HPC systems skyrockets with ever more compute intensive tasks, each subtask should be handled with near-optimal power efficiency. This necessarily means that the system has to adapt itself optimally to the current needs of the application. As a result, exascale HPC systems need to be heterogeneous and employ ultra-efficient compute nodes.

Limitations of Existing Reconfigurable Systems

Several run-time reconfigurable systems have been proposed over the years. However, several obstacles prevent them from becoming mainstream:

The tools required for programming such run-time reconfigurable systems still face substantial reconfiguration overheads, which prevent them from being used for largescale deployment;

The run-time reconfigurable systems have to use existing FPGA architectures, which are not specifically built with run-time reconfiguration in mind, and therefore lack in efficiency for maximally exploiting possible run-time reconfiguration benefits;

For newly proposed reconfigurable architectures, the optimal granularity of the reconfiguration infrastructure is still undecided. A low-level reconfiguration infrastructure (such as in current FPGAs) has higher flexibility but larger reconfiguration time, compared to a coarser granularity;

HPC applications are not optimized for exploiting the available reconfigurability. This is partly because current toolchains do not maximize programmability and designer productivity.

Research Objectives

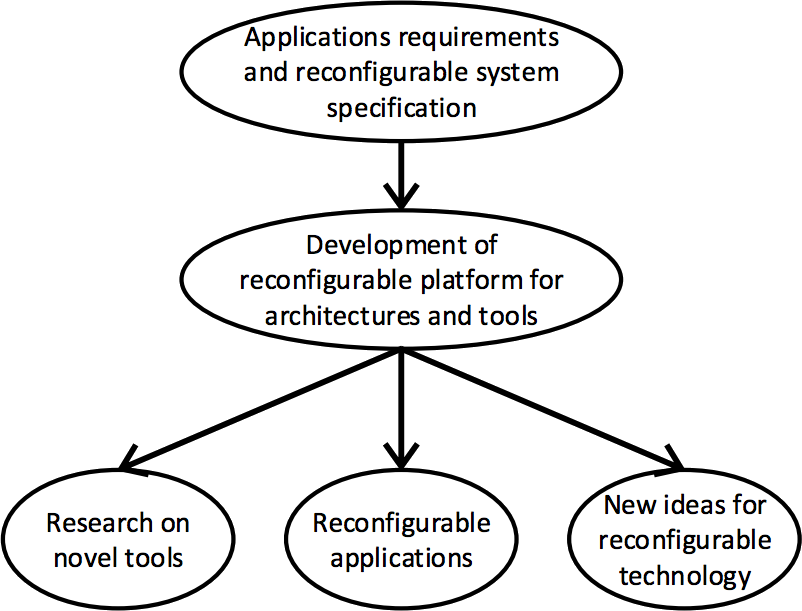

The main objective of the EXTRA project is to develop an open source research platform for continued research on reconfiguration architectures and tools.

KO1

KO2

KO3

Technical Objectives

To achieve these key objectives, we identified six major technical objectives that must be achieved.

- Enable a co-design approach for developing reconfigurable HPC architectures, tools and applications.

- Include reconfigurability as an explicit design concept in future HPC systems design.

- Speed up the reconfiguration process through novel reconfiguration approaches for processing, BRAMs, special blocks and interconnection in a coarse-grain reconfiguration architecture.

- Provide just-in-time synthesis methods for reconfiguration on the fly, based on application requirements.

- Improve the HPC applications under consideration.

- Suggest new reconfiguration features for future technologies.

Main Approach

The main assumption in the EXTRA project is that system reconfigurability will be a key concept in future HPC systems. In order to develop reconfigurable hardware HPC systems, we need (i) to design completely new system architectures that are inherently reconfigurable, (ii) to develop new tools that enable efficient reconfiguration, and (iii) to identify the applications that can best exploit this novel concept of reconfigurability.

The EXTRA project will tackle all three issues and propose initial architectures, tools and applications that benefit from reconfigurability.

In conclusion, this project focuses on the fundamental building blocks for run-time reconfigurable exascale HPC systems: new reconfigurable architectures with very low reconfiguration overhead, new tools that truly take reconfiguration as a design concept, and applications that are tuned to maximally exploit run-time reconfiguration techniques. The developed exploration platform ensures a smooth and efficient co-design of architecture, tools and applications.

© 2015-2026 EXTRA

The EXTRA project has received funding from the European Union Horizon 2020 Framework Programme (H2020-EU.1.2.2.) under grant agreement number 671653.